本帖最后由 天道无极 于 2012-2-16 21:00 编辑

http://www.eetrend.com/technology/100030594

Intel 22nm制程tri-gate晶体管实物

Inteltri-gate晶体管结构图

继四年前首度启用HKMG工艺制作商用处理器之后,全球最大的半导体厂商Intel又一次站在了业界前列,这一次他们用实际行动宣告与传统的平面型晶体管技术彻底告别。如先前外界所预料的那样,本周三Intel举办了一次新闻发布会,会上Intel高管Mark Bohr宣布Intel在22nm制程处理器中全面启用tri-gate晶体管技术,他并表示tri-gate晶体管技术的启用可以极大地减小晶体管的工作电压。

Bohr称:“转向立体型晶体管设计的最大好处是管子的工作电压和漏电流可以较大幅度地减小。”另外,他还表示制造tri-gate晶体管所用的晶圆成本仅比传统平面型晶体管高2-3%左右。

PS: Intel口中的tri-gate其实与人们通常所说的Finfet本质相同,有关tri-gate技术与Finfet技术读者可参考本站的这篇简介文章。

Bohr,Intel高级副总裁 Bill Holt以及架构总经理Dadi Perlmutter三人共同展示了在实际运行中的服务器,台式机以及笔记本,这些设备上均装用了22nm制程的Ivy Bridge处理器,这款处理器产品将于明年早些时候正式上市。

全面而非部分启用tri-gate技术:

与之前人们猜想的情况有所不同,Bohr在发布会上称Intel的22nm制程处理器中所有的晶体管均采用tri-gate制作,而此前人们猜想的情况是仅有SRAM部分采用了tri-gate,而逻辑电路部分仍采用传统的平面型晶体管结构。另外,Bohr还透露在Intel的22nm制程处理器中,有些部分的晶体管电路采用了6鳍设计(在Finfet中,Fin即鳍的部分相当于平面型晶体管中的沟道),而有些部分的晶体管电路则仅采用2鳍设计,举例而言,SRAM晶体管部分的晶体管结构便于逻辑晶体管的结构有所不同,在tri-gate的基础上做出了一些改动。

另外Bohr还表示,Intel在14nm节点仍将继续使用tri-gate晶体管技术,不过届时Intel可能会进一步增加tri-gate晶体管中鳍部分的高度,以增强管子的性能,另外芯片内含的晶体管密度也将比22nm节点大幅增加。

Bohr透露,Intel早已决定要在22nm节点放弃50年来人们一直在使用的平面型晶体管技术。Intel的tri-gate晶体管技术其实属于Finfet的一种变种,采用这种结构的晶体管其沟道垂直与衬底,沟道的三个面则被三个栅极围绕,这种结构可以增强栅极对沟道的控制作用,从而进一步提升管子的电流驱动能力和省电性能。

tri-gate晶体管的性能提升:

Intel公布的22nmtri-gate晶体管沟道电流值

与Intel目前最好的32nm制程工艺比较,22nm制程立体型晶体管工作电压Vdd仅0.7v,平面型晶体管则很难达到这样的工作电压水品,同时管子的性能则比前者提升37%。同时,管子的延迟时间可以在输入电压比32nm制程低0.2v(即0.8V)的条件下保持在原有的水平。

他说:“22nm制程tri-gate技术的晶体管性能基本与32nm制程一致,但输入电压仅0.8V,比后者的1.0V更低,这样工作状态下管子的功耗可减小50%以上。”

tri-gate与平面型体硅及FDSOI技术的优劣对比:

会上Bohr还简要介绍了一些晶体管器件物理学方面的知识。据他介绍,由于平面型体硅晶体管的衬底部分存在微小电压,因此很难优化管子的亚阀值(sub-threshold,台湾人的说法是次临界,即晶体管的栅电压低于门限电压的情况)性能。而FDSOI器件虽然可以解决这个问题,但是制造FDSOI器件的超薄体SOI晶圆成本太高。在谈到由意法半导体等公司主推的超薄体SOI技术时,Bohr则称由于这种SOI晶圆的埋入氧化层与其顶部超薄硅层之间的距离非常小,因此对超薄体SOI晶圆的制造技术提出了非常高的要求。

“虽然已经有人制造出这种超薄体SOI晶圆,但是其价格太高,而且制造难度也很大。”他并表示Intel认为这种超薄体SOI晶圆的最终成本可能会(比常规SOI)高出10%。与此类似,FDSOI阵营的成员也承认超薄体SOI的成本相对较高,但是他们强调FDSOI可以降低所需的隔离结构等的数量,因此FDSOI可以间接降低掩模板制作方面的成本,这里节省的成本则可以与晶圆增加的成本大致相抵。

Perlmutter则在会上表示,Intel的22nm产品输入电压将更低,而且同时与32nm平面型晶体管相比,22nmtri-gate晶体管功耗更低,晶体管面积则可减小一半左右。目前,Intel Atom系列SOC产品的使用率还不是很高,其主要的原因之一就是其对手基于ARM架构的SOC功耗相对更低。Perlmutter表示Intel将尽快将22nmtri-gate制程引入到Atom系列产品上,并称转换的步调要比从过去从45nm转换到32nm的步调更快。

tri-gate技术在实际产品上将如何部署:

据Intel透露,最先使用22nmtri-gate技术制作的处理器产品将是双核设计的Ivy Bridge处理器,不过Atom内核的产品也非常需要22nmtri-gate技术。“Atom方面的需求是非常迫切的。22nmtri-gate技术不仅省电,而且还可以给Atom系列产品带来更高的性能。”

VLSI Research市调公司的CEO Dan Hutcheson认为此次Intel转向tri-gate设计具有“历史性的意义”,是50多年前Bob Noyce, Jack Kilby等人发明首款平面型晶体管之后的又一次重要变革。Gartner公司的分析师Dean Freeman则干脆表示:“Intel这次干的太漂亮了!”

尽早转向Finfet技术“让Intel找到了移动设备市场的一个极好突破点,因为这种技术的省电性能极好,其性能表现则可以将ARM一族打得溃不成军。”

其它厂商在Finfet方面的动向:

除了Intel之外,ARM架构SOC的代工大厂台积电公司不久前也宣布会转向Finfet技术,不过按他们此前宣布的计划,要到14nm节点才会完成转型。至于IBM及其合作伙伴,Freeman认为他们同样不太可能在14nm节点之前转向Finfet技术。

制作tri-gate晶体管的技术难点:

Gartner的分析报告称要实现Finfet技术,需要克服许多制造技术方面的难关。比如要制造出Finfet晶体管,要求光刻机的图像对准性能较好。“过去人们认为只有采用EUV光刻机才有可能制造出Finfet晶体管,不过由于ASML或者尼康生产的193nm液浸式光刻机具有极高的套准精度(overlay),因此也有可能采用这种光刻机制造出Finfet晶体管。”

另外,尽管采用PIII(Plasma-immersion ion implantation)离子注入工艺可以实现,但如何保证Fin两侧漏源极侧墙部位从上到下杂质掺杂(目的是减小漏源极的电阻)密度的均匀性则是另外一个Finfet制造的难题。

此外,制造Finfet结构时蚀刻Fin时如何保证Fin侧壁的粗糙度控制在一定的水平之内则是另一个难题。

释疑:

英特尔公布重大技术,下一代处理器基于3D晶体管。那么,3D晶体管的精确定义及其重要性是什么呢?下面对此作出解答。3D的确切含义是什么?

英特尔称之为3D晶体管,但从技术上讲,这是三门()栅极 晶体管。传统的二维门由较薄的三维硅鳍所取代,硅鳍由硅基垂直伸出。

何谓硅鳍?

门包裹着硅鳍。硅鳍的三面都由门包裹控制,顶部包裹一个门,侧面各包裹一个门,共包裹三个门。2D二维晶体管只有顶部一个门包裹控制。英特尔对此解释简单明了:“控制门增加,晶体管处于‘开’状态时,通过的电流会尽可能多;处于‘关’状态时,电流会尽快转为零,能耗降至最低。晶体管在两种状态之间迅速切换能够显著提高性能。”

其重要性何在?

对证实摩尔定律至关重要。根据摩尔定律,每两年硅片设备上的晶体管数量翻番。随着设备尺寸日益缩小,按照传统二维方式增加晶体管数量已经不可能了。因此,3D或垂直晶体管就很有必要。英特尔不仅从理论上证明其可行性,还将制造基于3D晶体管的芯片。

英特尔距离采用该技术还有多远?

从本质上说,英特尔是一家制造商。因此,当该公司公布一项新技术时,绝对不是一个空中楼阁的创意。英特尔下一代处理器Ivy Bridge将独家采用该3D晶体管技术。也就是说,英特尔在生产Ivy Bridge芯片时将退出2D晶体管制造业务、完全转向3D晶体管。今年底,Ivy Bridge将进入商业生产,2012年进入批量生产。

22纳米的重要意义是什么?

Ivy Bridge将采用22纳米技术,当前Sandy Bridge处理器采用的是32纳米技术。除了上述3D晶体管成果外,采用较小的几何体通常能够提高处理器的速度和能效。

3D晶体管意味着产品速度更快吗?

当然,3D晶体管不仅意味着芯片速度更快、还意味着能效更高。英特尔面临的最大挑战不是速度,而是能效。3D晶体管能够使芯片在电压较低、泄漏较少的环境下运行,较之前的英特尔芯片性能更高、能效更好。

3D晶体管技术有助于英特尔在智能手机和平板电脑领域有效竞争吗?

从理论上可行。ARM公司目前是英特尔的新主要对手。ARM芯片用于全球大多数平板电脑和智能手机,主要原因是其能效高。英特尔22纳米3D晶体管技术性能较32纳米二维晶体管提高37%。英特尔表示:“这意味着3D晶体管适用于小尺寸的手持设备,反复开关消耗的能源较低。相同性能下,3D晶体管能耗不足32纳米二维晶体管的一半。”

英特尔三维晶体管背后的故事

英特尔刚刚公布的其最新三维晶体管设计,1999年始于加州大学伯克利分校实验室,是十余年以来研究和开发的顶峰。这种22纳米晶体管(英特尔表示它能使芯片速度提高37%并节约一半能量)将被用于英特尔各种22纳米芯片的产品中,包括逻辑和存储电路。采用“三维电子门(tri-gate)”的晶体管处理器已经在工作系统中得到证明,并且英特尔公司将于今年内下半年投入批量生产。设备制造商将如何利用这种芯片尚不清楚,但他们可能会以此延长移动设备的电池寿命并提高精密度,同样也会为台式机和服务器提供更快的处理速度。

提升:在传统晶体管中(左图),一个位于顶端的电子门控制着流经下方平面硅信道的电流。英特尔的最新设计中(右图),硅信道如鱼鳍般突起,因而电子门可以从三个方向联通。这为对流经信道的电流提供了更灵活的控制方法,并降低了能量泄露。

英特尔转向这一全新设计是由于现有设计已经开始遭遇瓶颈。传统晶体管是由安置在一块平面信道顶端一个名为电子门的金属结构构成的。这个电子门控制着经由该信道从源极流向漏极的电流。每一代芯片,其信道都会变得更小,使得像英特尔这样的公司能够通过集成更多的晶体管而制造出更快速的芯片。但对于电子门,要完全切断电流已经变得更加困难。无法完全关闭的漏电晶体管会浪费能量。

三栅极晶体管(tri-gate transistor)利用在芯片表面竖起的矩形硅信道,使得电子门可以从三个方向联通信道,而不只是一面。这种更为紧密的联系意味着电子门甚至在22纳米工艺下几乎可以完全关闭,这正是英特尔的新型芯片在效能方面获得提高的原因。同样有可能通过制造有着多个电子门彼此相连的硅信道的三栅极晶体管,以提高流经各晶体管的电流总量,从而获得更高的性能。

英特尔并不是这种设计的发明者,但却是首次将其应用于产品的公司。如果该公司在从32纳米向22纳米晶体管转型的过程中接受了平面晶体管,那么这种芯片将在效率和性能方面有20%到30%的提升,行业分析师莱恩里·格温耐普(Linley Gwennap)说。曾有推测表示该公司将仅会把这种新晶体管设计应用于存储元件而不是逻辑元件,因此并不会完全舍弃平面晶体管。通过将三栅极技术应用于存储和逻辑芯片,格温耐普说,“英特尔实际上正在冲击瓶颈并看到性能上的大幅提升,这或许会成为一个(超越其竞争对手的)巨大优势”。

这些三维晶体管最初是由三位加州大学伯克利分校的研究人员在上世纪90年代末设想并建造出来的,作为对美国防御远景研究规划局(United States Defense Advanced Research Projects Agency)的要求为设计25纳米以下晶体管的回应,这是小于当时产品中晶体管技术量级要求的。胡正明(Chenming Hu)在1996年飞往日本的途中为这种新型晶体管书写了技术说明。一个由胡、杰弗里•波哥(Jeffrey Bokor)和Tsu-Jae King Liu组成的小组首先在1999年制造出了这些被称作FinFET的晶体管。

“它当初大获成功,”胡说。在伯克利的研究人员继续对设计进行改进的同时,学校选择将此知识产权向公众发布而不是申请专利。胡曾向多个公司提出这一项目,包括英特尔。2002年,FinFET以及名为“绝缘硅(silicon on insulator)”的伯克利第二项设计被《国际半导体技术蓝图》(International Technology Roadmap of Semiconductors)誉为有可能满足行业今后15年需求的技术。但至少在英特尔, FinFET领先第二项设计,这种设计需要向晶体管中加入一层很薄的硅。大约两年前,生产硅晶圆的公司还不能使活动层足够薄。法国公司Soitec现在已经能够为这种设计制造出所需的晶圆,并且胡表示,英特尔的竞争对手可能会在某个时候采用它。

将三维晶体管器件设计从实验室转移到实际产品花费了大约十年时间。有关为制造新型芯片所要做的必要芯片升级的诸多细节英特尔并未透露。但基于对新材料和新机器无明显需要的事实,以及公司承诺产品成本仅有2%到3%的微弱上涨,改进似乎也不会太大。该公司已表示,制造三维晶体管信道仅需一道额外的蚀刻工序。

胡表示,伯克利的研究人员从开始就决定他们的最新设计将要与业内已有基础设备兼容,而且也证明事实如此。胡说,使该技术投入量产的主要障碍或许就是要解决可靠性问题:当数以亿计的极薄的三维信道制造在一块独立晶圆上时,要使它们可控。

胡说,伯克利小组设计了这些三极管,因此他们不需要电路设计师来完整地重新设计芯片架构。这是为什么英特尔能够如此之快地开发出产品的部分原因。在过去的五年里,胡的小组一直将电路模拟工具应用于三栅极晶体管。

然而,电路设计师们看到了可能由这些三极管带来的新机遇。他们为改变各电子门提供了新的方法,这“给了设计师们可以把玩的新玩意儿以进一步提高能效和可靠性,”斯坦福大学电气工程及计算机上科学教授萨巴辛·米特拉(Subhasish Mitra)说。看到一款全新的晶体管在约十年的时间跨度中投入量产是一个令人鼓舞的信号,表明这一行业“并没过时”,而且优秀的技术创意仍然可以从学术实验室中脱颖而出,米特拉补充到。

英特尔3D晶体管技术背后的奇人----胡正明(Chenming Hu) 教授

近日,英特尔发布的22nm 3D晶体管技术吸引了全球半导体业者的瞩目,这个技术也让一个华人获得了瞩目,他就是这个技术的发明人--胡正明教授,12年前,胡正明教授在加州大学领导着一个由美国国防部高级研究计划局(DARPA)出资赞助的研究小组,当时他们的研究目标是CMOS技术如何拓展到25nm领域,当时的研究结果显示有两种途径可以实现这种目的:一是立体型结构的FinFET晶体管,另外一种是基于SOI的超薄绝缘层上硅体技术 (UTB-SOI,也就是我们常说的FDSOI晶体管技术),FinFET晶体管与英特尔所推崇的3D晶体管及其类似,只是名称不同而已。

这是转自百度百科上有关胡正明教授的资料显示:

胡正明(Chenming Hu) ,微电子学家。美国国籍。1947年7月出生于中国北京。1973年获美国加州大学伯克利分校博士学位。现任美国加州大学伯克利分校杰出讲座教授、北京大学计算机科学技术系兼职教授、中国科学院微电子所荣誉教授、台湾交通大学(新竹)微电子器件荣誉教授、1991-1994年任清华大学(北京)微电子学研究所荣誉教授。1997年当选为美国工程科学院院士。2007年当选中国科学院外籍院士。

胡正明教授是微电子微型化物理及可靠性物理研究的一位重要开拓者,对半导体器件的开发及未来的微型化做出了重大贡献。主要科技成就为:

领导研究出BSIM,从实际MOSFET晶体管的复杂物理推演出数学模型,该数学模型于1997年被国际上38家大公司参与的晶体管模型理事会选为设计芯片的第一个且唯一的国际标准;发明了在国际上极受注目的FinFET等多种新结构器件;对微电子器件可靠性物理研究贡献突出:首先提出热电子失效的物理机制,开发出用碰撞电离电流快速预测器件寿命的方法,并且提出薄氧化层失效的物理机制和用高电压快速预测薄氧化层寿命的方法。首创了在器件可靠性物理的基础上的IC可靠性的计算机数值模拟工具。

1985年应严东生院士邀请,胡正明等三位美国科学家提出了发展我国微电子科学技术的战略性的重要咨询建议,对当时我国微电子科学技术的发展有较大影响。1981年以来与电子科技大学、中国科学院微电子所、北京大学、清华大学、复旦大学、浙江大学等校进行合作研究并作学术讲座,协助推动在中国召开国际会议。1990年在北大与清华设置五名研究生奖学金,并鼓励中国留学生回国发展半导体工业。

胡正明为国立台湾大学电机工程学士、柏克莱加大电机及计算机硕士、博士,曾任美国麻省理工学院电机及计算机系教授,并有多项学术荣誉:为美国国家工程院院士、柏克莱加州大学校长讲座教授、TSMC杰出讲座教授、国立交通大学名誉教授、IEEE Fellow、北京清华大学名誉教授、中华民国国科会第一届杰出讲座、柏克莱加州大学杰出教学奖等。

曾任台积电技术长的胡正明,被称为“台湾第一技术长”。这位“美国国家工程院院士”以“科学家”之姿,以最直接的方式贡献台湾半导体界,期间,并创下新竹科学园区有史以来,第一位获数理组院士的半导体业人士。

二00四年,胡正明重返柏克莱加大,结束他在台积电的一千个日子,回到学术界,现仍为台积电顾问。任教职之外,胡正明的产业经验不仅在台积电,也曾创办Celestry Design Technologies, Inc、并曾任国家半导体公司非挥发性记忆体研发经理,除了学术、产业的杰出表现之外,还当过旧金山东湾中文学校董事长。他在学术领域屡创高峰,在电晶体尺寸及性能研发上屡次创新世界纪录,也为积体电路设计订定出第一个国际标准电晶体模型。他拥有美国专利逾百项,期刊及会议文献发表约八百件。

胡教授及其团队成员发表了有关FinFET(1999年发布)和UTB-SOI(2000年发布)的技术文章后,大部分半导体厂商的开发工作方向转向了FinFET技术,因为他们都认为要想制造出UTB-SOI上如此薄的硅膜实在太困难了。

胡教授曾说:“我当时觉得我们恐怕没有办法搞到可以满足这种条件的SOI基体,没有公司能够对外供应硅膜厚度仅有5nm(50埃,仅相当12-15个硅原子的尺寸)的SOI晶圆。我当时觉得这不太可能实现,或者说等人们具备这种技术能力时,FinFET技术可能已经得到了充分的发展。不过两年前法国Soitec公司改变了这种情况,他们开始推出300mm UTB-SOI的晶圆样品,这些晶圆的顶层硅膜原始厚度只有12nm,然后再经处理去掉顶部的7nm厚度硅膜,最后便可得到5nm厚度的硅膜。这便为UTB-SOI技术的实用化铺平了道路。”

胡教授认为,FinFET和UTB-SOI技术是可以并存的,不过在未来几年内,两者都会想尽办法彼此超越对方成为主流技术。现在Intel采用了FinFET技术,原因是这种技术可以让微处理器的性能相对更强。他认为台积电公司会在14nm节点开始采用FinFET技术,然后则会为低功耗产品的用户推出应用了UTB-SOI技术的产品。而联电公司则会减轻对FinFET技术的投资力度,并直接转向UTB-SOI技术。

P.S.:第三代i3/i5/i7(3rd generation core i)将要在今年四月正式上市!

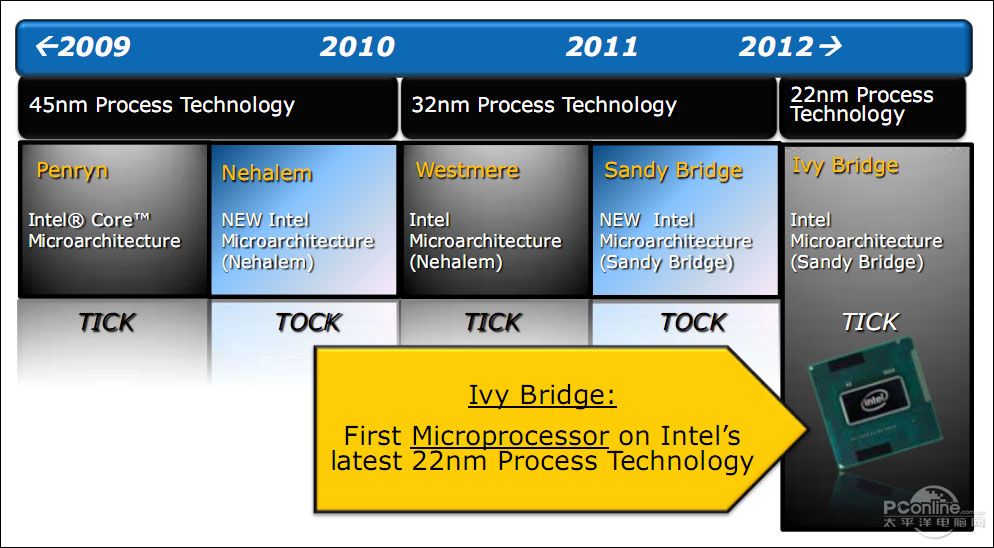

Tick-Tock更新模式,Sandy Bridge升级为Ivy Bridge

Tick-Tock更新模式,Sandy Bridge升级为Ivy Bridge

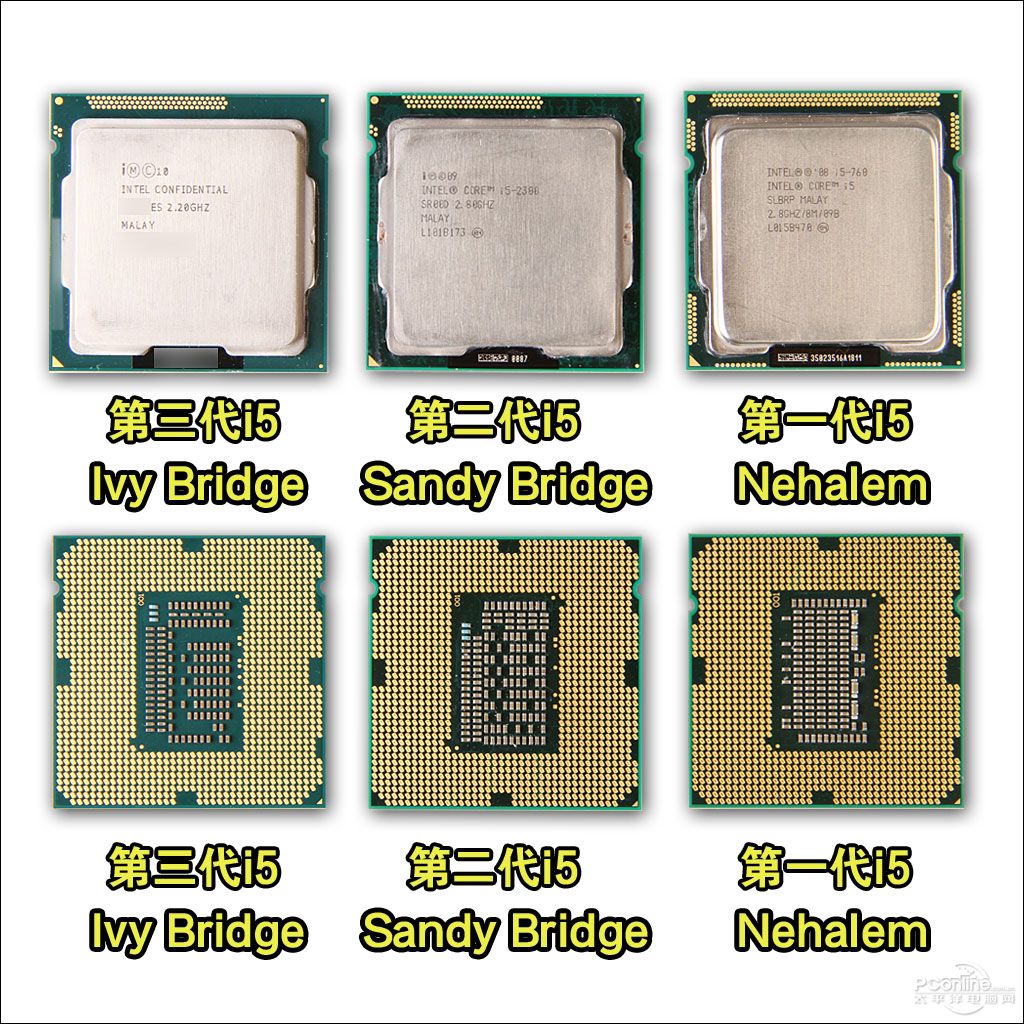

三代i5外观比较

三代i5外观比较

Finfet技术(3D晶体管)详解.rar

(574.84 KB, 下载次数: 6850)

Finfet技术(3D晶体管)详解.rar

(574.84 KB, 下载次数: 6850)

|